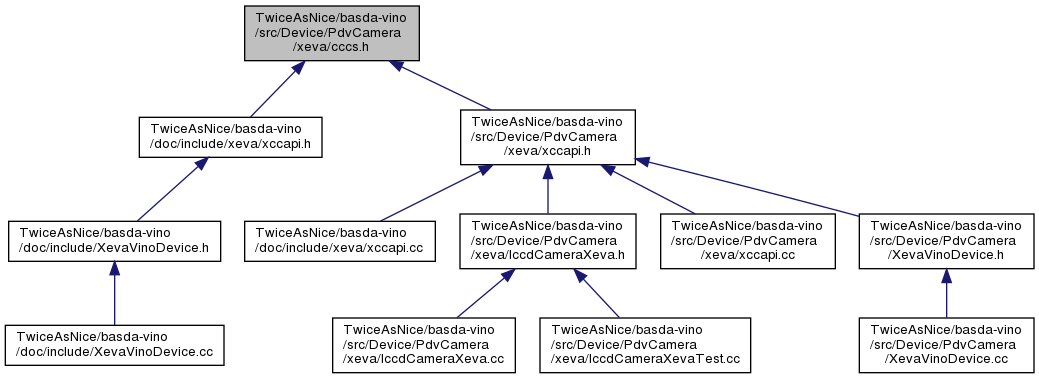

This graph shows which files directly or indirectly include this file:

Macros | |

| #define | B_CFGDATA 0x0000 |

| #define | B_UARTDATA 0x0100 |

| #define | B_SHORT 0x7fc0 |

| #define | B_NOP 0x7fff |

| #define | B_CONFIG 0x7ffe |

| #define | WOI_YSTART 0x8000 |

| #define | WOI_YEND 0x9000 |

| #define | WOI_XSTART 0xa000 |

| #define | WOI_XEND 0xb000 |

| #define | WOI_YINC 0xc000 |

| #define | WOI_XINC 0xd000 |

| #define | C_LAG0 0xe000 |

| #define | C_LAG1 0xe100 |

| #define | C_LAG2 0xe200 |

| #define | C_LAG3 0xe300 |

| #define | C_GAIN 0xe400 |

| #define | C_OFFSET 0xe500 |

| #define | C_MISC 0xe700 |

| #define | CC_SINGLESHOT 0x80 |

| #define | CC_DIAGNOSTIC 0x40 |

| #define | CC_DIAG_Y 0x20 |

| #define | CC_DIAG_XXORY 0x10 |

| #define | CC_16BIT_8BIT 0x08 |

| #define | CC_BIT_SHIFT_H 0x04 |

| #define | CC_BIT_SHIFT_M 0x02 |

| #define | CC_BIT_SHIFT_L 0x01 |

| #define | CC_SHIFT_0BITS 0x00 |

| #define | CC_SHIFT_1BITS 0x01 |

| #define | CC_SHIFT_2BITS 0x02 |

| #define | CC_SHIFT_3BITS 0x03 |

| #define | CC_SHIFT_4BITS 0x04 |

| #define | CC_SYNC1_EOF 0x00 |

| #define | CC_SYNC1_BOF 0x01 |

| #define | CC_SYNC1_EOL 0x02 |

| #define | CC_SYNC1_BOL 0x03 |

| #define | CC_SYNC2_EOF 0x00 |

| #define | CC_SYNC2_BOF 0x04 |

| #define | CC_SYNC2_EOL 0x08 |

| #define | CC_SYNC2_BOL 0x0c |

| #define | CC_F1000_SHY 0x80 |

| #define | C_ANAVAL0 0xe800 |

| #define | C_ANAVAL1 0xe900 |

| #define | C_ANAVAL2 0xea00 |

| #define | C_ANAVAL3 0xeb00 |

| #define | CSO_YDELAY 0xec00 |

| #define | CSO_XDELAY 0xed00 |

| #define | CSO_XDELAY2 0xee00 |

| #define | CSO_ADCDELAY 0xef00 |

| #define | C_ANASEL 0xf000 |

| #define | CSO_TDELAY 0xf100 |

| #define | CSO_PWM 0xf200 |

| #define | C_LINK 0xf300 |

| #define | I2CADDR 0xf400 |

| #define | I2CDATA 0xf500 |

| #define | C_LRATE0 0xf600 |

| #define | C_LRATE1 0xf700 |

| #define | C_LRATE2 0xf800 |

| #define | C_LRATE3 0xf900 |

| #define | C_START 0xff80 |

| #define | C_SYNCSTART 0xff81 |

| #define | C_WAIT 0xff82 |

| #define | C_START_WAIT 0xff83 |

| #define | C_SINGLE 0xff84 |

| #define | C_SYNCCONT 0xff85 |

| #define | C_CAL 0xff88 |

| #define | CC_SHORT 0xffc0 |

| #define | CC_NOP 0xffff |

| #define | CC_SYNC 0xfffe |

| #define | CC_RESET 0xfffd |

| #define | CC_ABORT 0xfffc |

| #define | I2CRDREQ 0xfffb |

| #define | I2CWRREQ 0xfffa |

| #define | I2CSTATRESET 0xfff9 |

| #define | CC_CTRL 0xffc0 |

| #define | CC_CTRL_AUTORESTART 0x0E |

| #define | CC_CTRL_DOUBLECLOCKING 0x06 |

| #define | AUX_ADDRESS (0xFC00) |

| #define | AUX_DATA (0xFD00) |

| #define | AUX_DATA_INC (0xFE00) |

Macro Definition Documentation

◆ AUX_ADDRESS

| #define AUX_ADDRESS (0xFC00) |

◆ AUX_DATA

| #define AUX_DATA (0xFD00) |

◆ AUX_DATA_INC

| #define AUX_DATA_INC (0xFE00) |

◆ B_CFGDATA

| #define B_CFGDATA 0x0000 |

◆ B_CONFIG

| #define B_CONFIG 0x7ffe |

◆ B_NOP

| #define B_NOP 0x7fff |

◆ B_SHORT

| #define B_SHORT 0x7fc0 |

◆ B_UARTDATA

| #define B_UARTDATA 0x0100 |

◆ C_ANASEL

| #define C_ANASEL 0xf000 |

◆ C_ANAVAL0

| #define C_ANAVAL0 0xe800 |

◆ C_ANAVAL1

| #define C_ANAVAL1 0xe900 |

◆ C_ANAVAL2

| #define C_ANAVAL2 0xea00 |

◆ C_ANAVAL3

| #define C_ANAVAL3 0xeb00 |

◆ C_CAL

| #define C_CAL 0xff88 |

◆ C_GAIN

| #define C_GAIN 0xe400 |

◆ C_LAG0

| #define C_LAG0 0xe000 |

◆ C_LAG1

| #define C_LAG1 0xe100 |

◆ C_LAG2

| #define C_LAG2 0xe200 |

◆ C_LAG3

| #define C_LAG3 0xe300 |

◆ C_LINK

| #define C_LINK 0xf300 |

◆ C_LRATE0

| #define C_LRATE0 0xf600 |

◆ C_LRATE1

| #define C_LRATE1 0xf700 |

◆ C_LRATE2

| #define C_LRATE2 0xf800 |

◆ C_LRATE3

| #define C_LRATE3 0xf900 |

◆ C_MISC

| #define C_MISC 0xe700 |

◆ C_OFFSET

| #define C_OFFSET 0xe500 |

◆ C_SINGLE

| #define C_SINGLE 0xff84 |

◆ C_START

| #define C_START 0xff80 |

◆ C_START_WAIT

| #define C_START_WAIT 0xff83 |

◆ C_SYNCCONT

| #define C_SYNCCONT 0xff85 |

◆ C_SYNCSTART

| #define C_SYNCSTART 0xff81 |

◆ C_WAIT

| #define C_WAIT 0xff82 |

◆ CC_16BIT_8BIT

| #define CC_16BIT_8BIT 0x08 |

◆ CC_ABORT

| #define CC_ABORT 0xfffc |

◆ CC_BIT_SHIFT_H

| #define CC_BIT_SHIFT_H 0x04 |

◆ CC_BIT_SHIFT_L

| #define CC_BIT_SHIFT_L 0x01 |

◆ CC_BIT_SHIFT_M

| #define CC_BIT_SHIFT_M 0x02 |

◆ CC_CTRL

| #define CC_CTRL 0xffc0 |

◆ CC_CTRL_AUTORESTART

| #define CC_CTRL_AUTORESTART 0x0E |

◆ CC_CTRL_DOUBLECLOCKING

| #define CC_CTRL_DOUBLECLOCKING 0x06 |

◆ CC_DIAG_XXORY

| #define CC_DIAG_XXORY 0x10 |

◆ CC_DIAG_Y

| #define CC_DIAG_Y 0x20 |

◆ CC_DIAGNOSTIC

| #define CC_DIAGNOSTIC 0x40 |

◆ CC_F1000_SHY

| #define CC_F1000_SHY 0x80 |

◆ CC_NOP

| #define CC_NOP 0xffff |

◆ CC_RESET

| #define CC_RESET 0xfffd |

◆ CC_SHIFT_0BITS

| #define CC_SHIFT_0BITS 0x00 |

◆ CC_SHIFT_1BITS

| #define CC_SHIFT_1BITS 0x01 |

◆ CC_SHIFT_2BITS

| #define CC_SHIFT_2BITS 0x02 |

◆ CC_SHIFT_3BITS

| #define CC_SHIFT_3BITS 0x03 |

◆ CC_SHIFT_4BITS

| #define CC_SHIFT_4BITS 0x04 |

◆ CC_SHORT

| #define CC_SHORT 0xffc0 |

◆ CC_SINGLESHOT

| #define CC_SINGLESHOT 0x80 |

◆ CC_SYNC

| #define CC_SYNC 0xfffe |

◆ CC_SYNC1_BOF

| #define CC_SYNC1_BOF 0x01 |

◆ CC_SYNC1_BOL

| #define CC_SYNC1_BOL 0x03 |

◆ CC_SYNC1_EOF

| #define CC_SYNC1_EOF 0x00 |

◆ CC_SYNC1_EOL

| #define CC_SYNC1_EOL 0x02 |

◆ CC_SYNC2_BOF

| #define CC_SYNC2_BOF 0x04 |

◆ CC_SYNC2_BOL

| #define CC_SYNC2_BOL 0x0c |

◆ CC_SYNC2_EOF

| #define CC_SYNC2_EOF 0x00 |

◆ CC_SYNC2_EOL

| #define CC_SYNC2_EOL 0x08 |

◆ CSO_ADCDELAY

| #define CSO_ADCDELAY 0xef00 |

◆ CSO_PWM

| #define CSO_PWM 0xf200 |

◆ CSO_TDELAY

| #define CSO_TDELAY 0xf100 |

◆ CSO_XDELAY

| #define CSO_XDELAY 0xed00 |

◆ CSO_XDELAY2

| #define CSO_XDELAY2 0xee00 |

◆ CSO_YDELAY

| #define CSO_YDELAY 0xec00 |

◆ I2CADDR

| #define I2CADDR 0xf400 |

◆ I2CDATA

| #define I2CDATA 0xf500 |

◆ I2CRDREQ

| #define I2CRDREQ 0xfffb |

◆ I2CSTATRESET

| #define I2CSTATRESET 0xfff9 |

◆ I2CWRREQ

| #define I2CWRREQ 0xfffa |

◆ WOI_XEND

| #define WOI_XEND 0xb000 |

◆ WOI_XINC

| #define WOI_XINC 0xd000 |

◆ WOI_XSTART

| #define WOI_XSTART 0xa000 |

◆ WOI_YEND

| #define WOI_YEND 0x9000 |

◆ WOI_YINC

| #define WOI_YINC 0xc000 |

◆ WOI_YSTART

| #define WOI_YSTART 0x8000 |

1.8.14

1.8.14