#include "PlxTypes.h"

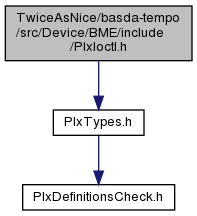

Include dependency graph for PlxIoctl.h:

Classes | |

| struct | _MANAGEMENTDATA |

| struct | _BUSIOPDATA |

| struct | _DMADATA |

| struct | _MISCDATA |

| struct | _IOCTLDATA |

Typedefs | |

| typedef struct _MANAGEMENTDATA | MANAGEMENTDATA |

| typedef struct _BUSIOPDATA | BUSIOPDATA |

| typedef struct _DMADATA | DMADATA |

| typedef struct _MISCDATA | MISCDATA |

| typedef struct _IOCTLDATA | IOCTLDATA |

| typedef enum _DRIVER_MSGS | DRIVER_MSGS |

Macro Definition Documentation

◆ PLX_IOCTL_ABORTADDR_READ

| #define PLX_IOCTL_ABORTADDR_READ IOCTL_MSG( MSG_ABORTADDR_READ ) |

◆ PLX_IOCTL_BUS_IOP_READ

| #define PLX_IOCTL_BUS_IOP_READ IOCTL_MSG( MSG_BUS_IOP_READ ) |

◆ PLX_IOCTL_BUS_IOP_WRITE

| #define PLX_IOCTL_BUS_IOP_WRITE IOCTL_MSG( MSG_BUS_IOP_WRITE ) |

◆ PLX_IOCTL_CHIP_TYPE_GET

| #define PLX_IOCTL_CHIP_TYPE_GET IOCTL_MSG( MSG_CHIP_TYPE_GET ) |

◆ PLX_IOCTL_COMMON_BUFFER_PROPERTIES

| #define PLX_IOCTL_COMMON_BUFFER_PROPERTIES IOCTL_MSG( MSG_COMMON_BUFFER_PROPERTIES ) |

◆ PLX_IOCTL_DEVICE_INIT

| #define PLX_IOCTL_DEVICE_INIT IOCTL_MSG( MSG_DEVICE_INIT ) |

◆ PLX_IOCTL_DMA_BLOCK_CHANNEL_CLOSE

| #define PLX_IOCTL_DMA_BLOCK_CHANNEL_CLOSE IOCTL_MSG( MSG_DMA_BLOCK_CHANNEL_CLOSE ) |

◆ PLX_IOCTL_DMA_BLOCK_CHANNEL_OPEN

| #define PLX_IOCTL_DMA_BLOCK_CHANNEL_OPEN IOCTL_MSG( MSG_DMA_BLOCK_CHANNEL_OPEN ) |

◆ PLX_IOCTL_DMA_BLOCK_TRANSFER

| #define PLX_IOCTL_DMA_BLOCK_TRANSFER IOCTL_MSG( MSG_DMA_BLOCK_TRANSFER ) |

◆ PLX_IOCTL_DMA_CONTROL

| #define PLX_IOCTL_DMA_CONTROL IOCTL_MSG( MSG_DMA_CONTROL ) |

◆ PLX_IOCTL_DMA_SGL_CLOSE

| #define PLX_IOCTL_DMA_SGL_CLOSE IOCTL_MSG( MSG_DMA_SGL_CLOSE ) |

◆ PLX_IOCTL_DMA_SGL_OPEN

| #define PLX_IOCTL_DMA_SGL_OPEN IOCTL_MSG( MSG_DMA_SGL_OPEN ) |

◆ PLX_IOCTL_DMA_SGL_TRANSFER

| #define PLX_IOCTL_DMA_SGL_TRANSFER IOCTL_MSG( MSG_DMA_SGL_TRANSFER ) |

◆ PLX_IOCTL_DMA_STATUS

| #define PLX_IOCTL_DMA_STATUS IOCTL_MSG( MSG_DMA_STATUS ) |

◆ PLX_IOCTL_DOORBELL_READ

| #define PLX_IOCTL_DOORBELL_READ IOCTL_MSG( MSG_DOORBELL_READ ) |

◆ PLX_IOCTL_DOORBELL_WRITE

| #define PLX_IOCTL_DOORBELL_WRITE IOCTL_MSG( MSG_DOORBELL_WRITE ) |

◆ PLX_IOCTL_DRIVER_VERSION

| #define PLX_IOCTL_DRIVER_VERSION IOCTL_MSG( MSG_DRIVER_VERSION ) |

◆ PLX_IOCTL_EEPROM_PRESENT

| #define PLX_IOCTL_EEPROM_PRESENT IOCTL_MSG( MSG_EEPROM_PRESENT ) |

◆ PLX_IOCTL_EEPROM_READ

| #define PLX_IOCTL_EEPROM_READ IOCTL_MSG( MSG_EEPROM_READ ) |

◆ PLX_IOCTL_EEPROM_READ_BY_OFFSET

| #define PLX_IOCTL_EEPROM_READ_BY_OFFSET IOCTL_MSG( MSG_EEPROM_READ_BY_OFFSET ) |

◆ PLX_IOCTL_EEPROM_WRITE

| #define PLX_IOCTL_EEPROM_WRITE IOCTL_MSG( MSG_EEPROM_WRITE ) |

◆ PLX_IOCTL_EEPROM_WRITE_BY_OFFSET

| #define PLX_IOCTL_EEPROM_WRITE_BY_OFFSET IOCTL_MSG( MSG_EEPROM_WRITE_BY_OFFSET ) |

◆ PLX_IOCTL_HS_ID_READ

| #define PLX_IOCTL_HS_ID_READ IOCTL_MSG( MSG_HS_ID_READ ) |

◆ PLX_IOCTL_HS_NCP_READ

| #define PLX_IOCTL_HS_NCP_READ IOCTL_MSG( MSG_HS_NCP_READ ) |

◆ PLX_IOCTL_HS_STATUS

| #define PLX_IOCTL_HS_STATUS IOCTL_MSG( MSG_HS_STATUS ) |

◆ PLX_IOCTL_INTR_ATTACH

| #define PLX_IOCTL_INTR_ATTACH IOCTL_MSG( MSG_INTR_ATTACH ) |

◆ PLX_IOCTL_INTR_DETACH

| #define PLX_IOCTL_INTR_DETACH IOCTL_MSG( MSG_INTR_DETACH ) |

◆ PLX_IOCTL_INTR_DISABLE

| #define PLX_IOCTL_INTR_DISABLE IOCTL_MSG( MSG_INTR_DISABLE ) |

◆ PLX_IOCTL_INTR_ENABLE

| #define PLX_IOCTL_INTR_ENABLE IOCTL_MSG( MSG_INTR_ENABLE ) |

◆ PLX_IOCTL_INTR_STATUS_GET

| #define PLX_IOCTL_INTR_STATUS_GET IOCTL_MSG( MSG_INTR_STATUS_GET ) |

◆ PLX_IOCTL_INTR_WAIT

| #define PLX_IOCTL_INTR_WAIT IOCTL_MSG( MSG_INTR_WAIT ) |

◆ PLX_IOCTL_IO_PORT_READ

| #define PLX_IOCTL_IO_PORT_READ IOCTL_MSG( MSG_IO_PORT_READ ) |

◆ PLX_IOCTL_IO_PORT_WRITE

| #define PLX_IOCTL_IO_PORT_WRITE IOCTL_MSG( MSG_IO_PORT_WRITE ) |

◆ PLX_IOCTL_MAILBOX_READ

| #define PLX_IOCTL_MAILBOX_READ IOCTL_MSG( MSG_MAILBOX_READ ) |

◆ PLX_IOCTL_MAILBOX_WRITE

| #define PLX_IOCTL_MAILBOX_WRITE IOCTL_MSG( MSG_MAILBOX_WRITE ) |

◆ PLX_IOCTL_MU_INBOUND_PORT_READ

| #define PLX_IOCTL_MU_INBOUND_PORT_READ IOCTL_MSG( MSG_MU_INBOUND_PORT_READ ) |

◆ PLX_IOCTL_MU_INBOUND_PORT_WRITE

| #define PLX_IOCTL_MU_INBOUND_PORT_WRITE IOCTL_MSG( MSG_MU_INBOUND_PORT_WRITE ) |

◆ PLX_IOCTL_MU_OUTBOUND_PORT_READ

| #define PLX_IOCTL_MU_OUTBOUND_PORT_READ IOCTL_MSG( MSG_MU_OUTBOUND_PORT_READ ) |

◆ PLX_IOCTL_MU_OUTBOUND_PORT_WRITE

| #define PLX_IOCTL_MU_OUTBOUND_PORT_WRITE IOCTL_MSG( MSG_MU_OUTBOUND_PORT_WRITE ) |

◆ PLX_IOCTL_PCI_BAR_GET

| #define PLX_IOCTL_PCI_BAR_GET IOCTL_MSG( MSG_PCI_BAR_GET ) |

◆ PLX_IOCTL_PCI_BAR_MAP

| #define PLX_IOCTL_PCI_BAR_MAP IOCTL_MSG( MSG_PCI_BAR_MAP ) |

◆ PLX_IOCTL_PCI_BAR_RANGE_GET

| #define PLX_IOCTL_PCI_BAR_RANGE_GET IOCTL_MSG( MSG_PCI_BAR_RANGE_GET ) |

◆ PLX_IOCTL_PCI_BAR_UNMAP

| #define PLX_IOCTL_PCI_BAR_UNMAP IOCTL_MSG( MSG_PCI_BAR_UNMAP ) |

◆ PLX_IOCTL_PCI_BOARD_RESET

| #define PLX_IOCTL_PCI_BOARD_RESET IOCTL_MSG( MSG_PCI_BOARD_RESET ) |

◆ PLX_IOCTL_PCI_DEVICE_FIND

| #define PLX_IOCTL_PCI_DEVICE_FIND IOCTL_MSG( MSG_PCI_DEVICE_FIND ) |

◆ PLX_IOCTL_PCI_REG_READ_UNSUPPORTED

| #define PLX_IOCTL_PCI_REG_READ_UNSUPPORTED IOCTL_MSG( MSG_PCI_REG_READ_UNSUPPORTED ) |

◆ PLX_IOCTL_PCI_REG_WRITE_UNSUPPORTED

| #define PLX_IOCTL_PCI_REG_WRITE_UNSUPPORTED IOCTL_MSG( MSG_PCI_REG_WRITE_UNSUPPORTED ) |

◆ PLX_IOCTL_PCI_REGISTER_READ

| #define PLX_IOCTL_PCI_REGISTER_READ IOCTL_MSG( MSG_PCI_REGISTER_READ ) |

◆ PLX_IOCTL_PCI_REGISTER_WRITE

| #define PLX_IOCTL_PCI_REGISTER_WRITE IOCTL_MSG( MSG_PCI_REGISTER_WRITE ) |

◆ PLX_IOCTL_PHYSICAL_MEM_ALLOCATE

| #define PLX_IOCTL_PHYSICAL_MEM_ALLOCATE IOCTL_MSG( MSG_PHYSICAL_MEM_ALLOCATE ) |

◆ PLX_IOCTL_PHYSICAL_MEM_FREE

| #define PLX_IOCTL_PHYSICAL_MEM_FREE IOCTL_MSG( MSG_PHYSICAL_MEM_FREE ) |

◆ PLX_IOCTL_PHYSICAL_MEM_MAP

| #define PLX_IOCTL_PHYSICAL_MEM_MAP IOCTL_MSG( MSG_PHYSICAL_MEM_MAP ) |

◆ PLX_IOCTL_PHYSICAL_MEM_UNMAP

| #define PLX_IOCTL_PHYSICAL_MEM_UNMAP IOCTL_MSG( MSG_PHYSICAL_MEM_UNMAP ) |

◆ PLX_IOCTL_PM_ID_READ

| #define PLX_IOCTL_PM_ID_READ IOCTL_MSG( MSG_PM_ID_READ ) |

◆ PLX_IOCTL_PM_NCP_READ

| #define PLX_IOCTL_PM_NCP_READ IOCTL_MSG( MSG_PM_NCP_READ ) |

◆ PLX_IOCTL_POWER_LEVEL_GET

| #define PLX_IOCTL_POWER_LEVEL_GET IOCTL_MSG( MSG_POWER_LEVEL_GET ) |

◆ PLX_IOCTL_POWER_LEVEL_SET

| #define PLX_IOCTL_POWER_LEVEL_SET IOCTL_MSG( MSG_POWER_LEVEL_SET ) |

◆ PLX_IOCTL_REGISTER_READ

| #define PLX_IOCTL_REGISTER_READ IOCTL_MSG( MSG_REGISTER_READ ) |

◆ PLX_IOCTL_REGISTER_WRITE

| #define PLX_IOCTL_REGISTER_WRITE IOCTL_MSG( MSG_REGISTER_WRITE ) |

◆ PLX_IOCTL_VPD_ID_READ

| #define PLX_IOCTL_VPD_ID_READ IOCTL_MSG( MSG_VPD_ID_READ ) |

◆ PLX_IOCTL_VPD_NCP_READ

| #define PLX_IOCTL_VPD_NCP_READ IOCTL_MSG( MSG_VPD_NCP_READ ) |

◆ PLX_IOCTL_VPD_READ

| #define PLX_IOCTL_VPD_READ IOCTL_MSG( MSG_VPD_READ ) |

◆ PLX_IOCTL_VPD_WRITE

| #define PLX_IOCTL_VPD_WRITE IOCTL_MSG( MSG_VPD_WRITE ) |

Typedef Documentation

◆ BUSIOPDATA

| typedef struct _BUSIOPDATA BUSIOPDATA |

◆ DMADATA

◆ DRIVER_MSGS

| typedef enum _DRIVER_MSGS DRIVER_MSGS |

◆ IOCTLDATA

| typedef struct _IOCTLDATA IOCTLDATA |

◆ MANAGEMENTDATA

| typedef struct _MANAGEMENTDATA MANAGEMENTDATA |

◆ MISCDATA

Enumeration Type Documentation

◆ _DRIVER_MSGS

| enum _DRIVER_MSGS |

1.8.14

1.8.14